概要

ドイチュとジョサは、量子コンピュータを用いることで、従来のコンピュータより圧倒的に速く計算が行える問題を最初に発見しました。この問題を解く手順(アルゴリズム)は、ドイチュ-ジョサのアルゴリズムと呼ばれています。

ドイチュ-ジョサの問題とは、あるビット配列 $X$ のパターンが以下のどちらであるかを判定する問題です。

- パターンⅠ:全て「0」または全て「1」

- パターンⅡ:「0」と「1」の数が同数

上記以外のパターンは考えないとする前提ですので、この問題の実用性については不明ですが、量子コンピュータの高速性が最初に証明された問題です。

量子回路

量子コンピュータで行う演算は大きく3つの段階があります。

- 量子の重ね合わせの状態を作る

- 重ね合わせの状態で並列処理を行う

- 結果を取り出す

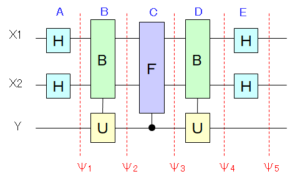

この2つ目の並列処理が、量子コンピュータが圧倒的に高速である秘密です。この処理を実現する量子回路は以下になります。ここでは4ビットの配列 $X$ のパターンを検索する回路を例にとります。

この図の、入力側の $x_1,x_2$ はアドレスビットで、$y$ は1ビットのレジスタです。4ビットの配列 $X$ は[B]に格納されており、2ビットのアドレスにより配列 $X$ の所定のビットを指定することができます。

[H]はアダマールゲート、[U]は制御ユニタリゲート、[F]は制御位相シフトを表します。操作Bと操作Dは、配列 $X$ の所定のビットが制御ビット、レジスタが標的ビットです。操作Cは、レジスタビットによりアドレスビットの位相が操作されます。

5つの操作の内、操作Aで量子ビットの重ね合わせの状態を作り、操作Bでビット読み出しの並列処理を行い、操作C~操作Eで一意的な結果を取り出します。具体的な動作は後で説明します。尚、各量子ビットの入力(初期状態)は、全て0であると仮定します。

$$\Psi_0=\ket{x_1x_2,y}=\ket{00,0}$$

そして、操作A~Dを行い、最後の $\Psi_5$ で $\ket{00}$ 以外の項が残るかどうかで、パターンⅠかパターンⅡかの判断を行います。

- パターンⅠ:全て「0」または全て「1」

⇒ $\Psi_5$ に $\ket{00}$ の項のみ残る - パターンⅡ:「0」と「1」の数が同数

⇒ $\Psi_5$ に $\ket{00}$ の項以外も残る

アルゴリズムの説明

操作A:重ね合わせの状態を作る

操作Aのアダマールゲートは、量子ビットに対し以下の操作を行います。

$$H\ket{0}=\frac{1}{\sqrt{2}}(\ket{0}+\ket{1})$$$$H\ket{1}=\frac{1}{\sqrt{2}}(\ket{0}-\ket{1})$$

そのため、

$$H\ket{00,0}=\frac{1}{2}(\ket{0}+\ket{1})\otimes(\ket{0}+\ket{1}) \otimes\ket{0}$$

これを計算すると以下のように、4ビットに相当するアドレスビットのパターンが生成されます。

$$\Psi_1=\frac{1}{2}(\ket{00,0}+\ket{01,0}+\ket{10,0}+\ket{11,0})$$

操作B:配列Xを読み出す

操作Bでは、各アドレスに相当するビットをレジスタビットで読み出します。例えばビット列が[1111](パターンⅠ)と[0110](パターンⅡ)の場合では $\Psi_2$ は以下になります。

- パターンⅠ:$X=[1111]$$$\Psi_2=\frac{1}{2}(\ket{00,1}+\ket{01,1}+\ket{10,1}+\ket{11,1})$$

- パターンⅡ:$X=[0110]$$$\Psi_2=\frac{1}{2}(\ket{00,0}+\ket{01,1}+\ket{10,1}+\ket{11,0})$$

操作Bは制御ユニタリゲートで、アドレスビットで指定された配列 $X$ のビットが「1」の場合はレジスタビットが反転($y=1$)し、「0」の場合は保持($y=0$)されます。結果として、4ビットの配列 $X$ のレジスタへの読み出しが1回で(並列で)行われています。

操作C:結果を取り出す(1)

操作Cは制御位相シフトゲートで、レジスタビットが「1」の場合に、位相を反転(符号を反転)させます。2つのビットパターンで具体的に書くと以下になります。

- パターンⅠ:$X=[1111]$$$\Psi_3=\frac{1}{2}(-\ket{00,1}-\ket{01,1}-\ket{10,1}-\ket{11,1})$$

- パターンⅡ:$X=[0110]$$$\Psi_3=\frac{1}{2}(\ket{00,0}-\ket{01,1}-\ket{10,1}+\ket{11,0})$$

操作D:結果を取り出す(2)

操作Bと同様に、アドレスビットで指定された配列 $X$ のビットが「1」の場合はレジスタビットが反転し、「0」の場合は保持されます。結果として、レジスタビットは初期状態(0)に戻ります。

- パターンⅠ:$X=[1111]$$$\Psi_4=\frac{1}{2}(-\ket{00,0}-\ket{01,0}-\ket{10,0}-\ket{11,0})$$

- パターンⅡ:$X=[0110]$$$\Psi_4=\frac{1}{2}(\ket{00,0}-\ket{01,0}-\ket{10,0}+\ket{11,0})$$

操作E:結果を取り出す(3)

次の操作Dでは、再度アダマールゲートを通します。アダマールゲートは各アドレスに対して以下のような変換を行います。

$$H\ket{00}=\frac{1}{2}(\ket{0}+\ket{1})\otimes(\ket{0}+\ket{1})=\frac{1}{2}(\ket{00}+\ket{01}+\ket{10}+\ket{11})$$$$H\ket{01}=\frac{1}{2}(\ket{0}+\ket{1})\otimes(\ket{0}-\ket{1})=\frac{1}{2}(\ket{00}-\ket{01}+\ket{10}-\ket{11})$$$$H\ket{10}=\frac{1}{2}(\ket{0}-\ket{1})\otimes(\ket{0}+\ket{1})=\frac{1}{2}(\ket{00}+\ket{01}-\ket{10}-\ket{11})$$$$H\ket{11}=\frac{1}{2}(\ket{0}-\ket{1})\otimes(\ket{0}-\ket{1})=\frac{1}{2}(\ket{00}-\ket{01}-\ket{10}+\ket{11})$$

これを $\Psi_4$ の式に代入して計算します。

- パターンⅠ:$X=[1111]$

この場合は、$\ket{00}$ の項のみ残ります。$$\Psi_5=\frac{1}{4}\Big(-(\ket{00}+\ket{01}+\ket{10}+\ket{11})\otimes\ket{0}$$$$-(\ket{00}-\ket{01}+\ket{10}-\ket{11})\otimes\ket{0}$$$$-(\ket{00}+\ket{01}-\ket{10}-\ket{11})\otimes\ket{0}$$$$-(\ket{00}-\ket{01}-\ket{10}+\ket{11})\otimes\ket{0}\Big)$$$$=-\ket{00}\otimes\ket{0} -①$$ - パターンⅡ:$X=[0110]$

この場合は、$\ket{00}$ 以外の項が残ります。$$\Psi_5=\frac{1}{4}\Big((\ket{00}+\ket{01}+\ket{10}+\ket{11})\otimes\ket{0}$$$$-(\ket{00}-\ket{01}+\ket{10}-\ket{11})\otimes\ket{0}$$$$-(\ket{00}+\ket{01}-\ket{10}-\ket{11})\otimes\ket{0}$$$$+(\ket{00}-\ket{01}-\ket{10}+\ket{11})\otimes\ket{0}\Big)$$$$=\ket{11}\otimes\ket{0} -②$$

ビット判定の仕組み

①と②についてアドレスビットの項を書き出すと以下になります。

| $+/-$ | $+\ket{00}$ | $+\ket{01}$ | $+\ket{10}$ | $+\ket{11}$ |

| $+/-$ | $+\ket{00}$ | $-\ket{01}$ | $+\ket{10}$ | $-\ket{11}$ |

| $+/-$ | $+\ket{00}$ | $+\ket{01}$ | $-\ket{10}$ | $-\ket{11}$ |

| $+/-$ | $+\ket{00}$ | $-\ket{01}$ | $-\ket{10}$ | $+\ket{11}$ |

パターンⅠの場合は、[0000]か[1111]のどちらかですが、その場合は1列目が全てプラスか全てマイナスになりますので、2列目の $\ket{00}$ の項が残り、3~5列目は消去されることが分かります。

パターンⅡの場合は、「0」と「1」が混在し、1列目はプラスとマイナスが混在するため、どのような組み合わせであっても $\ket{00}$ 以外の項(3~5列目)が必ず残ることになります。

ステップ数の比較

ドイチュ-ジョサの問題を従来のコンピュータで解く場合、ビット配列を端から1つづつ確認する必要があります。例えば、4ビット(=$2^2$ ビット)の場合、2ビットを確認して全て「0」でも、たまたまである可能性もあるので、まだパターンⅠがパターンⅡかの判断はできません。

そのため、必ずビット数の半分より1つ多い回数(2+1回)確認する必要があります。一般に、$2^N$ ビットの配列の場合は、$2^{N-1}+1$ 回のステップが必要になります。

一方、量子回路のステップ数を数えると、操作Aでは2つのアダマールゲートがあるので2ステップ、操作B~Dは3ステップ、操作Eは操作Aと同様2ステップで、合計7ステップとなります。

これはビット配列の数は4ビット($=2^2$)の場合ですが、ビット配列が増えても、操作Aと操作Eのステップ数は増えるのみで、操作B~Dのステップ数は変わりません。一般に $2^N$ ビット配列の場合は、ステップ数は $2N+3$ 程度になります。

従来のコンピュータと量子コンピュータのステップ数を、ビット数ごとに比べると以下になります。

| ビット数 | ステップ数 | $2^2(4)$ | $2^5(32)$ | $2^{10}(1024)$ | $2^{20}$ |

| 従来コンピュータ | ~$2^{N-1}+1$ | 3 | 17 | 513 | 523,288 |

| 量子コンピュータ | ~$2N+3$ | 7 | 13 | 23 | 43 |

このように、ビット数が増えた場合は、量子コンピュータでは圧倒的に少ないステップ数で計算を完了させることができます。